本文来源:智车科技 作者:刘洪

/ 导读 /

半年前,要找车规5nm芯片只有恩智浦(NXP)曾宣布下一代汽车芯片选用台积电5nm制程,预计2021年秋交付首批样片;今天却已不只一个,2018年7月高通收购NXP失败,现在也挺进了5nm车规芯片,产品有望最快在2023年底量产上市;特斯拉也在备战“芯片升级”,与三星电子合作为全自动驾驶开发5nm芯片。

刚刚,IT行业5nm芯片被曝集体翻车余音未了,车规5nm芯片又甚嚣尘上了。汽车芯片真的进入了5nm时代?我们来分析一下,这炙手可热的车规5nm芯片究竟货色如何?

5nm集体“发烧”为哪般?

和手机、电脑等设备相比,汽车运行环境的恶劣程度不是一点半点,尤其是热环境。现实是,别说车规,就是消费设备用的5nm也还存在问题。因为10年前困扰台积电和三星的问题又回来了。

5nm是目前EUV(极紫外线)光刻机能实现的最先进芯片制程,也是手机厂商的重要卖点,2020年下半年,苹果A14、麒麟9000、骁龙888等5nm制程芯片相继面世。不过,公开信息显示,上述芯片无一幸免被曝实际功耗不低,发热未减:“一度达80℃”、“发热降频”、“变身火龙”、“高烧不退”。一时间,5nm芯片集体翻车成为热议。

厂商一直在追随甚至想超越摩尔定律,遇到的最大问题是芯片内部的晶体管漏电。进入深亚微米制造制程时代之前,动态功耗一直是芯片设计的焦点,而在深亚微米制程,动态功耗在总功耗中的比例越来越小,静态功耗比例则越来越大;进入纳米时代,漏电流功耗对整个功耗的影响变得非常显著。在90nm制程电路中,静态功耗可以占到总功耗40%以上。

为什么呢?原来集成电路每一代制造制程的进步都是由缩短CMOS晶体管的沟道长度实现的。不断缩短沟道长度使电源电压、阈值电压、栅极氧化层厚度等制程参数随之按比例缩小,而短沟道效应(SCE)、栅极隧穿电流、结反偏隧穿电流等漏电流机制越来越显著,引起芯片漏电流功耗的上升。另外,沟道长度越短,漏电流功耗增加越快。

在5nm制程之前,因为采用了当时创新的FinFET(鳍式场效应晶体管)来替代传统平面式晶体管,台积电、三星和英特尔都成功抑制了漏电流功耗。

智能坐舱vs自动驾驶

2015年开始,高通切入智能座舱和自动驾驶市场,近年来凭借其SoC芯片的强大算力,其14nm骁龙820A座舱SoC已经拿下不少客户,甚至成了2020年不少中高端车型的标配。

2019 CES展上,高通发布基于台积电第一代7nm制程的第一款车规级数字座舱SoC骁龙SA8155,入局车载市场。其强大之处在于优秀的运算能力和协同匹配能力,高通将其定义为“一机多屏多系统”的终极解决方案。今年伊始曝光谍照的长城WEY全新车型将是首款搭载8155的量产车型。

那么,智能座舱和自动驾驶能否相提并论呢?答案是否定的,前者与后者高度相关,但不可等同。智能座舱主要包括高清显示、仪表、主动安全报警(驾驶员监控)、实时导航、在线信息娱乐、紧急救援、车联网以及人机交互系统(语音识别、手势识别)等。其主要作用在于通过改变人机交互方式,提升驾驶者和乘员体验,有助于将产品属性升级为服务属性。毫无疑问,人工智能(AI)将赋能人车交互的智能化升级。智能座舱在半导体技术的支持下还是比较容易一步步实现。

制程和用途与芯片算力参考示例

自动驾驶呢?应该没有马斯克说的那么容易在不久的将来就能实现。因为它涉及的问题实在是太多了。就说芯片的算力吧,不可与智能座舱同日耳语。据称,高通8155芯片CPU处理器和GPU图形处理器算力是同级产品的3-5倍。而CES 2020上发布基于5nm制程Snapdragon Ride自动驾驶平台核心SoC基础算力为10TOPS,其中单颗SoC支持NCAP标准下的L1/L2级自动驾驶,多颗SoC组合可以实现L4级自动驾驶,最大算力可达700TOPS以上。

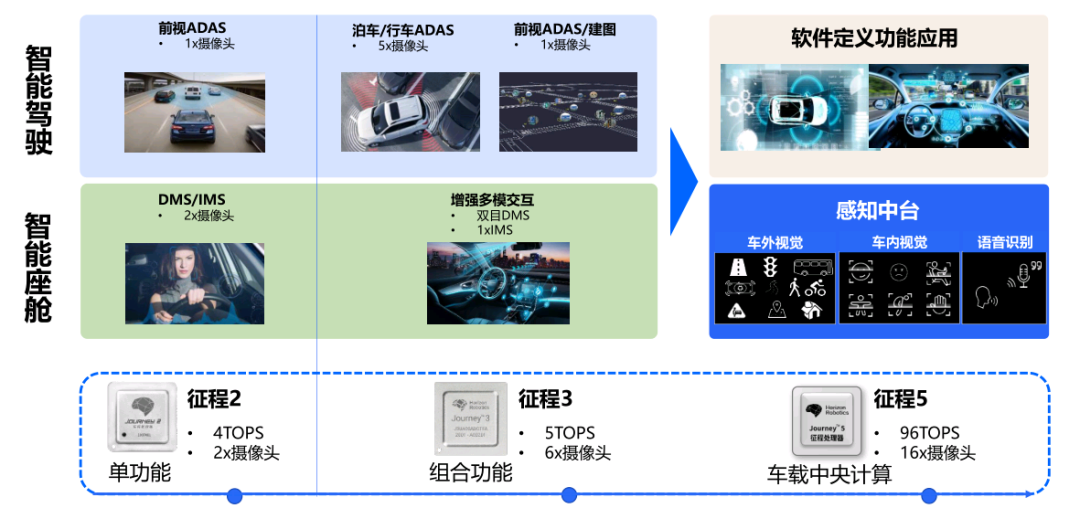

2020年11月,华为智能驾驶专家电话会议纪要中关于芯片的讨论就很能说明问题:“自动驾驶未来需要大算力芯片,市场一是自动驾驶,二是智能座舱。智能座舱里也会有很多人工智能应用,比如语音识别,以前用科大讯飞的方案是在云端做,体验感很差。现在用智能座舱芯片,像高通或华为基本上都有七八个T算力,地平线也一样,其征程二也有大概6个T算力(实际上是4TOPS)。大算力计算芯片一定是一个大趋势,也是一个门槛……自动驾驶有三个核心要素,第一是数据,第二是场景,第三是算力。特斯拉已经远超国内的自己在那里吹牛逼的公司了。”

1 2 下一页>